|

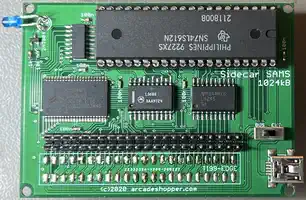

ACHTUNG: Hier wird der SAMS Sidecar mit 1MB RAM besprochen.

Das SAMS, Nachfolger des AMS (oder AEMS, je nach Lesart) verwendet einen TI 74LS612 Memory Mapper zu dem Zweck,

für den er gedacht ist...😉 - mit anderen Worten: nichts Aufregendes! | |||||||||||||||||||||

Funktionsweise des LS612 | |||||||||||||||||||||

|

Der LS612 gehört zu einer Reihe von 'Memory Mappern', die vom LS610 bis zum LS613 reicht,

wobei die Unterschiede in dem Typ der Ausgangsschaltung (Tri-State vs. Open Collector)

und deren Betriebsart (Transparent bzw. Latch) liegen.

Der LS612 besitzt transparente Tri-State Ausgänge. Das Funktionsprinzip ist so einfach wie undurchsichtig... wobei sich der LS612 zwischen den Adressbus der CPU und einen um ein vielfaches größeren Speicher stellt, in dem er den originären Speicher der CPU abbildet. Er tut dies, indem er die obersten 4 Adressbits eines Mikroprozessors durch bis zu 12 Bits ersetzt, die aus einem von 16 Mapping Registern kommen, welche mit den genannten 4 Bits adressiert werden. Der LS612 ist also im Grunde genommen nur ein schnelles 16x12 RAM (70ns Delay über alles!), dessen Adressierung über 4 Bit erfolgt, und dessen 12 Datenleitungen als zusätzliche Adressleitungen für das erweiterte RAM verwendet werden. Im Fall des TI bzw. des SAMS wird diese Aussage etwas konkreter:

|

| ||||||||||||||||||||

Ansteuerung im TI-99/4A | |||||||||||||||||||||

Im vorigen Abschnitt wurden schon ein paar Aspekte angesprochen, wie sich das SAMS in den TI-Speicher einordnet,

daher wird jetzt die praktische Anwendung beschrieben.

Das SAMS besitzt keine eigene DSR, belegt aber die CRU-Basisadresse >1E00 um den Zugriff auf die Mapping-Register freizugeben.

CRU-Bit 0 aktiviert den Zugriff auf die insgesamt 8 verfügbaren Register, die an den Adressen >4004->401E liegen.

Da nur die von der 32kB-Erweiterung belegten Bereiche gemappt werden können bzw. dürfen, ergibt sich folgende Zuordnung:

Übrigens: Beim Hardware-Reset des LS612 werden alle Page-Register gelöscht und der Map-Mode ist deaktiviert. Hier ein paar einfache Beispiele: * * Bestimmte Mapping-Seite setzen * SETPGE LI R12,>1E00 SAMS Basisadresse MOVB @PGENUM,R0 Seitennummer (0-255) MOV @MEMRGE,R1 Memory Range nach R1, >2000->F000 SRL R1,11 Offset in die Registerliste (12 Bit runter fuer 4K und 1 hoch wegen des 2er Abstands) SB0 0 Zugriff auf die Map-Register aktivieren MOVB R0,@>4000(R1) Page festlegen SBZ 0 Map-Register wieder ausblenden RT und zurueck von wo immer wir her kamen * * Mapping Mode aktivieren * MAPON LI R12,>1E00 SAMS Basisadresse SBO 1 Mapping Mode an RT und weg * * Mapping Mode deaktivieren * MAPOFF LI R12,>1E00 SAMS Basisadresse SBZ 1 Mapping Mode aus RT und wegRecht hilfreich ist auch der SAMS Guide von Lee Stewart. | |||||||||||||||||||||

Die Hardware | |||||||||||||||||||||

Auf der PCB tummeln sich insgesamt 5 Käferchen:

ABER: Schnelle RAMs dieser Ära bzw. Technologie brauchen VIEL Strom, was man an der spürbaren Erwärmung des LS612 erkennen kann (die Gesamtverlustleistung beträgt knapp 1 Watt!). Wenn man also weitere Sidecars anstöpseln will, die über den Erweiterungsport versorgt werden sollen, sollte man sich vorher überlegen, ob das praktikabel ist. |

| ||||||||||||||||||||

| Kontakt: {anyname}@{use_the_url}.net |

Alle Bilder auf diesen Webseiten wurden von mir erstellt. Findet ihr sie anderswo, wurden sie hier geklaut! |

Letzte Aktualisierung: 2026-01-11 CW |